Récupération de Data Clock (RDC)

De nombreux flux de données numériques à haute vitesse, tels que l’Ethernet, sont transmis sans aucune information d’horloge spécifique. Ainsi, l’extrémité réceptrice doit générer une horloge d’entrée basée sur les données reçues. En pratique, une boucle à verrouillage de phase (PLL) se synchronise sur les transitions des données entrantes et un signal d’horloge approprié peut être extrait. L’horloge récupérée est également utilisée pour recadrer les données entrantes. Ce processus est appelé Récupération de l’horloge et des données (CDR).

Le flux de données doit être codé de manière à ce que des transitions de données suffisantes soient présentes dans le flux (c’est-à-dire pour réduire le nombre de symboles de données identiques consécutifs). Un schéma de codage courant est le codage 64B/66B.

L’objectif principal lors de la transmission d’un signal optique/électrique d’un point à un autre est de conserver l’intégrité du signal afin d’éviter toute perte de données. Une caractéristique clé est la capacité de transférer les informations de synchronisation d’un point source à un point de destination. Cette fonctionnalité de synchronisation est appelée Récupération de l’horloge et des données.

Qu’est-ce que la Récupération de l’horloge et des données ?

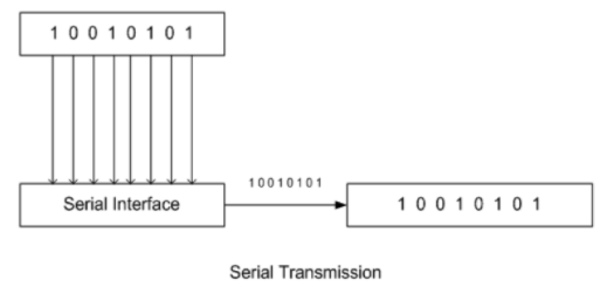

Les émetteurs-récepteurs optiques et électriques utilisent ce que l’on appelle la communication de données série. Dans ce type de communication, les bits de données sont transmis séquentiellement un par un.

Les transceivers optiques et électriques utilisent ce qu’on appelle la communication de données série. Dans ce type de communication, les bits de données sont transmis séquentiellement un par un.

La plupart des transceivers disponibles sur le marché aujourd’hui n’ont pas d’entrée d’horloge dédiée, ce qui signifie que des fonctions telles que la récupération de l’horloge et le recadrage des données sont réalisées à l’extérieur du transceiver (c’est-à-dire sur la carte hôte). Le côté récepteur doit alors récupérer l’horloge pour échantillonner les données arrivant sur les lignes série.

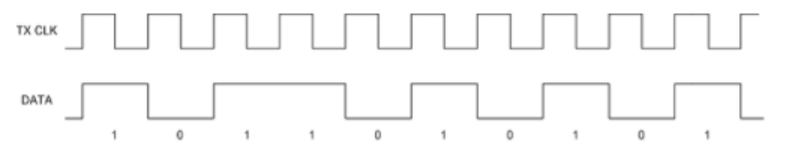

Pour ce faire, le côté récepteur a besoin d’une horloge d’une fréquence approximativement égale à celle des données entrantes. Une horloge récupérée est générée en alignant en phase l’horloge de référence sur les transitions du signal de données entrantes. Cela s’appelle la Récupération de l’horloge (Clock Recovery).

Le recadrage des signaux de données entrants en utilisant l’horloge récupérée s’appelle la Récupération des données (Data Recovery). Ensemble, cela constitue la Récupération de l’horloge et des données, ou CDR.

En d’autres termes, le rôle du CDR est de récupérer les informations de synchronisation à partir d’un signal entrant sans signal d’horloge accompagnant et de recadrer les données reçues.

Comment fonctionne le CDR ?

Détection de fréquence

Il verrouille sur une fréquence qui est récupérée à partir du flux de données entrant. Pour ce faire, il détecte les transitions de données et verrouille un VCO (Oscillateur Contrôlé en Tension) sur cette fréquence. Cette fréquence est ensuite utilisée lors de la génération du flux de bits de données transmis.

Pour simplifier, la fréquence Rx (horloge de destination) doit être la même que la fréquence Tx (horloge source).

Pour faciliter la détection de fréquence côté RX, la source de données envoie une séquence spécifique de bits, appelée séquence d’entraînement, avant de transmettre le flux de données réel. La séquence d’entraînement est très dense, ce qui permet au récepteur de verrouiller facilement la fréquence en vérifiant les ondes de données consécutives sur le fil avant le début des données valides.

Séquence d’entraînement idéale

2. Alignement de phase

Il ajuste la phase de l’horloge, déjà récupérée lors de la détection de fréquence, avec le flux de bits de données entrant. Il ajuste continuellement l’horloge en fonction des variations dans le flux de données entrant.

Ci-dessous se trouvent les transceivers Skylane avec CDR intégré :

- SPP85P300H0C

- SPP130100H0C

- SPP130020H0C

- SPP130400H0C

- SPP150400H0C

- SPP150800H0C

- SPCxx0400H0C

- SPCxx0700H0C

- XFP130100H0C

- XFP130200H0D

- XFP150400H0D

- XFP150800H0D

Source: protocol-debug.com